AN CONNECTOD PUBLICATION

Signal Integrity, Part 1 of 3 by Barry Olney p.24

ALSO:

Thermal Characterization of LEDs: Enabling the Upcoming Lighting Revolution by Dr. John Parry p.34

# SIGNAL INTEGRITY

# PCB BUYERScompare nearly 1900 manufacturers now at *The* PCB List.

Quick Search

**Advanced Search**

The best way to find a PCB fabricator, anywhere.

## **DESIGN NEWS**

### DFX — Design for Excellence

### Technical education with a design focus

# PCB Carolina in Raleigh, NC Presented by the IPC Designers Council Chapter This full day of education, vendor exhibition, and networking includes breakfast, luncheon, and an evening reception ... all free to attendees. February 20–26, 2015 IPC APEX EXPO in San Diego, CA Premier industry event features a range of design offerings • Professional development courses — three hours of classroom instruction led by SMEs • Design Forum — a day of technical presentations from thought leaders in design • Designer Certification

### **IPC Designer Certification**

CID (Certified Interconnect Designer-Basic) and CID+ (Advanced) are valuable professional credentials, earned in three-day sessions that include classroom instruction and testing.

### **USA** sessions

| October 15–17        | CID          | Manchester, NH and Redmond, WA                  |

|----------------------|--------------|-------------------------------------------------|

| October 21–23        | CID          | San Diego, CA                                   |

| November 6–8         | CID and CID+ | Raleigh, NC in conjunction with PCB Carolina    |

| December 3–5         | CID+         | Redmond, WA                                     |

| February 20–22, 2015 | CID and CID+ | San Diego, CA in conjunction with IPC APEX EXPO |

For USA sessions register at +1-800-643-7822.

New edition of CID and CID+ course materials will be available starting January 2015.

### If you are not already Certified:

Be sure to include the program in your budget for next year — contact your training center for information about class schedule and fees.

# Manufacturability Guidelines for all Phases of Product Development

This full-day technical course provides real-world guidelines for application of industry standards from design phase through to field testing: DFM (Design For Manufacturing), DFR (Design For Reliability), DFA (Design For Assembly) and more.

Every team involved in product realization will benefit from this course, led by experts with global consulting practices in manufacturability.

To schedule a session for your team — at your facility — contact Anne Marie Mulvihill, IPC Design Programs Manager at +1 847-597-2827.

IPC Designers Council

Members Only

SUBSCRIBE

An international society for individuals with interest in design.

No fees, only benefits — like discounts on designated IPC documents.

Already in Designers Council? Be sure you can access the

IPC technical forum for designers worldwide — subscribe at left.

### This Issue: SIGNAL INTEGRITY

### **FEATURED CONTENT**

Gone are the days when signal integrity was just a problem for the EE; if you don't already have signal integrity problems, you certainly will. In this issue, Yuriy Shlepnev and Barry Olney offer some of the latest SI tips, tricks and techniques for achieving signal integrity. We'll also feature columns by Charles Pfeil, John Coonrod, Tim Haag, Bob Tarzwell and Dan Beaulieu, and an article on Thermal Characterization of LEDs by John Parry of Mentor Graphics.

### 12 Sink or Swim at 28 Gbps

by Yuriy Shlepnev

### **FEATURE COLUMN**

### 24 Signal Integrity, Part 1 of 3

# Low-loss Laminate Materials for RF/Microwave/Millimeter-wave Designs

For over 100 years, Isola has been driving technology forward while improving end-product design with topperforming laminate and prepregs.

Our legacy continues with global R&D pushing our product line to the forefront in demanding RF/microwave designs.

With 10 manufacturing sites around the world, global quickturn capability, world-class technical service, measurement & modeling capabilities, and industry leading material development capabilities - Isola is well positioned to be your preferred RF/microwave partner.

The newest members of Isola's growing RF/Microwave laminate family now includes Terra Green™. a halogen-free, very low-loss, thermoset material that is available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

Astra®MT is a revolutionary ultra low-loss thermoset laminate replacement for PTFE, suitable for automotive radar, mm-wave and AESA applications.

I-Tera MT is available in core thicknesses from 0.002" to 0.018" and offers 18 different prepregs for optimal design flexibility.

I-Tera®MT RF is available in 20 and 30 mil cores and a 3.38 and 3.45 Dk.

|                                                                                                                                                                                                                                              | TerraGreen™     | Astra® MT       | I-Tera® MT/<br>I-Tera MT RF | IS680                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------------------|------------------------------------------|--|--|

| Tg                                                                                                                                                                                                                                           | 200°C           | 200°C           | 200°C                       | 200°C                                    |  |  |

| Td                                                                                                                                                                                                                                           | 390°C           | 360°C           | 360°C                       | 360°C                                    |  |  |

| DK @ 10 GHz                                                                                                                                                                                                                                  | 3.45            | 3.00            | 3.45                        | 2.80 - 3.45                              |  |  |

| Df @ 10 GHz                                                                                                                                                                                                                                  | 0.0030          | 0.0017          | 0.0031                      | 0.0028 - 0.0036                          |  |  |

| CTE Z-axis (50 to 260°C)                                                                                                                                                                                                                     | 2.90%           | 2.90%           | 2.80%                       | 2.90%                                    |  |  |

| T-260 & T-288                                                                                                                                                                                                                                | >60             | >60             | >60                         | >60                                      |  |  |

| Halogen free                                                                                                                                                                                                                                 | Yes             | No              | No                          | No                                       |  |  |

| VLP-2 (2 micron Rz copper)                                                                                                                                                                                                                   | Standard        | Standard        | Available                   | Available                                |  |  |

| Stable Dk and Df over the temperature range                                                                                                                                                                                                  | -55°C to +125°C | -40°C to +140°C | -55°C to +125°C             | -55°C to +125°C                          |  |  |

| Optimized Global constructions for Pb-Free<br>Assembly                                                                                                                                                                                       | Yes             | Yes             | Yes                         | Yes                                      |  |  |

| Compatible with other Isola products for<br>hybrid designs                                                                                                                                                                                   | Yes             | Yes             | Yes                         | For use in double-<br>sided applications |  |  |

| Low PIM < -155 dBc                                                                                                                                                                                                                           | Yes             | Yes             | Yes                         | Yes                                      |  |  |

| NOTE: Dk Df is at one resin %. The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms and conditions |                 |                 |                             |                                          |  |  |

of the agreement under which they are sold.

### FREE WEBINAR

### PCB Material Selection for RF/Microwave/Millimeter-wave Design

This webinar will educate you on how to select the appropriate PCB material for RF, microwave and millimeterwave applications through careful consideration of cost constraints and system-performance parameters, such as the frequency of operation and bandwidth, the electrical size of board and its critical features, loss and uniformity requirements, temperature range of system operation, and thermal and processing considerations.

OCTOBER 2014

**VOLUME 3**

NUMBER 10

MAGAZINE thepcbdesignmagazine.com

THE OPTIMUM

**MAGAZINE**

**DEDICATED TO**

**PCB DESIGN**

AN CONNECTOR PUBLICATION

### CONTENTS

### **ARTICLE**

### **34** Thermal Characterization of LEDs: **Enabling the Upcoming Lighting** Revolution

by Dr. John Parry

### **COLUMNS**

8 So You Want to Write an Article! by Andy Shaughnessy

- 42 This is Sketch Routing, Part 2: Quality by Charles Pfeil

- 46 Chilling Out with Conductive Adhesives by John Coonrod

52 Tarzwell's First—and Last— **Lean Meeting**

by Bob Tarzwell & Dan Beaulieu

58 Blink and You Will Miss It by Tim Haaq

### **VIDEO INTERVIEWS**

### **30 Embedded Components Standard Update**

### 49 IBM Seeking the Next Generation of Technologists

#### **SHORT**

49 New Mechanism of Photoconduction for Next-gen Devices

### **NEWS HIGHLIGHTS**

- 32 PCB007

- 50 Mil/Aero007

- 62 PCBDesign007

### **EXTRAS**

- **64** Events Calendar

- 65 Advertiser Index & Masthead

# **Engineering And Providing Balanced Interconnect Solutions**

### Flexible Printed Circuits • Rigid Flex • Wire Harnesses • Complete Assemblies

Our products and services are specifically designed to empower our customers to produce a product with superior performance and quality, as well as lower design, assembly, and system installation costs.

Partnering With Your Engineering Team To Deliver The Best Solution

...connecting technology

### THE SHAUGHNESSY REPORT

## So You Want to Write an Article!

by Andy Shaughnessy

I-CONNECT007

As a journalist and editor, I can't imagine a better beat to cover than PCB design and EDA. This is the perfect career for me. I come armed with an English degree. I studied Chaucer and Shakespeare for years to prepare myself for through-holes and fanout routing.

"I bear a charmed life," as Macbeth put it. But it's people like you who write the fantastic articles and columns that make our publications great. We'd be nowhere without these wonderful writers who sacrifice their nights and weekends putting their thoughts on paper.

That said, this month I'm going to offer a few tips for anyone considering writing articles or contributing press releases to this magazine, or any B2B pub, for that matter.

### **Spell Check is Your Friend**

We try to leave your copy as untouched as possible. We want your particular tone to shine through. But we also want all of our magazines to adhere to the same style. We follow the Associated Press style for the most part, but AP doesn't cover certain terms, such as microvia vs micro via vs micro-via. (We've settled on microvia, since that's how most of the industry spells it.)

Our writers keep us on our toes. Some of our contributors capitalize words for no reason, such as High-Density Interconnect. That's not a proper name, so it doesn't need to be capped. Other writers only capitalize every Noun, as if we were speaking high German. And beware the writer who has—recently—discovered the dash; the same holds true for the semicolon. It could be great stuff; then again, it might be trouble.

And some articles have obviously never been run through spell check. I use spell check, and so should you. It won't catch your use of "threw" instead of "through," but it will catch the biggest snafus, and it highlights sentences that are unclearly worded.

# THE BRAND NEW **HIGH PRODUCTIVITY** DATA MANAGING **SMART DOCUMENTING** LIBRARY BUILDING OrCAD PRODUCTS

## The Latest From the Greatest

OrCAD® has a history of delivering cutting edge products. Whether it is leading the desktop PCB revolution with OrCAD Capture or defining the standard for SPICE simulation and virtual prototyping with PSpice, OrCAD consistently stands at the forefront of desktop PCB design. We are proud to announce a new set of OrCAD technologies designed to improve productivity, reduce errors, enable collaboration, and help you deliver innovative products on time and on budget.

See demos of the new products: View Demos >

### **SO YOU WANT TO WRITE AN ARTICLE!** continues

### Have a Plan Before You Begin

If you're brave enough to submit an article, congratulations. We salute you! We won't get very far without good, solid content.

Before you begin, read some similar articles in the magazine you're submitting to, and develop a good understanding about the mag's audience. I've gotten articles from PR managers who have obviously never read my magazine. Our audience doesn't design ICs, but I still get articles about how to use the latest synthesis compiler to great advantage.

Sketch out a basic outline before you start writing your article. Take a few minutes to decide what you're trying to say. Why are you saying it? Is it important to a PCB designer, in our case? What will the reader learn?

### **Avoid Marketing Copy**

It may sound counterintuitive, but it's true: You're more likely to generate leads for your company if you keep marketing copy out of your article.

If you find yourself mentioning your company's "industry-leading software that easily and simply allows designers to simulate the most complex high-speed designs," you've become a marketing guy (or girl).

This is for your benefit, and mine. Marketing buried in an article makes readers angry, especially designers, because they're being marketed to constantly anyway. They expect our technical articles to be free of marketing spiels. They'll send me hate mail and they'll be mad at you and your company, and they won't forward your article to their friends.

I'm going to edit out all the marketing copy, though we do allow one mention of a company or tool as an example in the article. But you're much better off focusing on telling a story about laying out the board, performing EMC measurement, or describing the return of outsourced designs from Asia, and keeping the marketing out.

When in doubt, remember: Cover the process, not the tools or services.

### We Love Case Studies, But...

Case studies offer some of the best content around. A good case study explains how a company or department solved a major technical problem that was costing them time

and money. But I doubt we've run more than a handful in the past five years. Why?

Too often, the case study is just a big ad for a software tool or board shop. An EDA company or board shops asks a customer to write a case study, and it arrives in my inbox. The article reads great, for a while. Then, towards the end, when the future of the republic hangs in the balance, the customer buys the newest rev of an EDA tool, or sends his design to Fabricator XYZ, and their problems disappear into the vapor. All that's missing is a farmer shouting, "Hallelujah! Call the bank, Ma! We don't have to sell the farm after all!"

No, a case study is about much more than making the right tool purchase or picking the right board shop, though that may be one small part of the story. In a case study, readers want the dirty details. They want to hear about the process itself and all the attendant problems.

What were some of the problems you had before making this transition? What were some of the challenges to implementing this new process? What mistakes did you make? (That's a big plus.) Did you form different teams and divide the work? How did you assign members to the teams? How often did you meet to compare notes?

I'd love to run more case studies, so keep them in mind.

### Precise, But Concise

As the Bard said, "Brevity is the soul of wit." This means saying all that you need to say, and in as few words possible.

### **SO YOU WANT TO WRITE AN ARTICLE!** continues

Keep it concise and precise. Say what you need to say, and stop writing. Here are a few slightly exaggerated composites of sentences I've seen.

- The challenges PCB designers and engineers face are often challenging to PCB designers and engineers.

- Smaller North American printed circuit board fabricators and medium-sized North American printed circuit board fabricators can often learn from larger North American printed circuit board fabricators.

- The industry's problems can be very, very problematic.

- Your department will never have a proper process in place unless you create a process.

These sound silly, don't they? But I see this kind of thing every so often. If you're in doubt, read your complete draft out loud. Or have your spouse read it; many of our contributors utilize their spouses for copy editing. If your wife is like my exes, she won't mind telling you that you've made a mistake or two.

### The "So What?" Test

Once you're finished writing, the "So what?" test comes into play. Think about it: if a designer reads your article, is he likely to say, "So what? Every designer knows that."

Or will a designer say, "Wow, I didn't know that. This guy is quite intelligent, and he really keeps his thumb on the pulse of the industry. I'll read his stuff every time. I'll consider his company the next time I need new software, fabrication, or design services, or whatever his company offers."

Obviously, you can't write about a technological breakthrough in every article. But you don't have to. The good thing about designers is that you all have a different take on every subject.

In our case, we love columns, first-person screeds that allow (require, actually) the writer to share his personal feelings on the topic. Putting yourself into the story gets other designers interested. There's an old saying in journalism: People like reading about other people. Talk about how you overcame a certain hurdle.

Explain how you had a problem fanning out from a monster BGA, but you won the day by doing this, this, and this. Readers like a good story about trials and tribulations. Give it to them.

### **Press Release 101**

We post dozens of news stories each day, most of which arrive as press releases. If you're sending a press release to the media, don't forget to include times, dates, prices, and other relevant information. I still get PRs lacking these items.

Remember: Send press releases whenever you do anything, and I mean anything. Some of the larger EDA companies send out a PR if they hire a new janitor, and that's fine. I'd rather have too many press releases to choose from than too few.

Released a new product? Hired a new designer, EE, or sales manager? That's a PR. And think of it this way: You didn't just hire a new designer. No, your company is in a growth period, and the constant stream of new customers has made it imperative that you expand your staff. That new product is the first of many as you lead the industry into the future, etc.

For a good PR, give a summary of the news in the first paragraph. This should be followed by a quote from the CEO or CTO about how great this news is for you and your customers. (As I said, people love people, and press releases with quotes get more hits than those without quotes.) Finally, the last few paragraphs break down the details of the new tool or new hire. Don't forget an "About the Company" tagline at the end, including a company URL.

I hope this helps those of you considering writing for us. We'd love to have you on board. If you have any questions, give me a shout. See you next month! **PCBDESIGN**

Andy Shaughnessy is managing editor of *The PCB Design Magazine*. He has been covering PCB design for 15 years. He can be reached by clicking here.

### by Yuriy Shlepnev

SIMBERIAN INC.

### **Abstract**

How do you know that your signal integrity software is qualified for the analysis of interconnects with signals running at 28-32 Gbps? The software vendor told you so? How does the vendor know? Most of the time, it is a "sink or swim" situation for the SI software user. One way to figure it out is to use a validation platform, such as Wild River Technology's CMP-28/32 Channel Modeling Platform, which provides interconnect structures specifically designed to benchmark the signal integrity software at these data rates. Just run the post-layout analysis of interconnects on the validation platform and compare with the pre-qualified measurements taken by an expert up to 50 GHz. The validation process may be that simple in general, but some peculiarities are discussed in this article.

### Introduction

Design of PCB and packaging interconnects for data links running at 28-32 Gbps bitrates and beyond is a challenging problem, to say the least. It requires accurate electromagnetic analysis over extremely broad frequency bandwidth from DC to 40-50 GHz. What complicates it further is the absence of the broadband frequency-continuous dielectric and conductor roughness models. In addition, the final board is not usually manufactured as designed due to uncontrolled variations and manipulations by the board manufacturers to "dial in the impedance."

It is also extremely difficult to make highquality measurements up to 50 GHz. So is it possible to design and manufacture interconnects and have acceptable analysis-to-measurement correlation up to 40–50 GHz systematically? To answer, four necessary elements for design success were formulated [1]. One of the elements is systematic benchmarking of manufacturing, measurement, and the software. Systematic in

## A HIGHER DEGREE OF THERMAL CONDUCTIVITY, WHERE AND WHEN YOU NEED IT.

|        | Thermal<br>Conductivity | Ceramic<br>Filled | Fully<br>Formable | Non-Glass<br>Reinforced | Halogen<br>Free |

|--------|-------------------------|-------------------|-------------------|-------------------------|-----------------|

| VT-44A | 1.0W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4A1 | 1.6W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4A2 | 2.2W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4B1 | 1.0W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4B3 | 3.0W/m.K.               | <b>V</b>          |                   |                         |                 |

| VT-4B5 | 4.2W/m.K.               | <b>/</b>          |                   |                         |                 |

| VT-4B7 | 6.5W/m.K.               |                   |                   |                         |                 |

**VIEW THERMAL MANAGEMENT PRODUCTS**

Wherever technology takes you, we deliver.

this context means analysis-to-measurement correlation is observed, not just for one or two structures (test coupons for instance), but rather for a broad range of typical interconnects: single-ended and differential, stripline and microstrip, simple planar and with the vertical transitions or vias, etc.

Such comparison should be done consistently both in frequency (magnitude and phase of S-parameters) and time (TDR and eye diagram) domains. In other words, the system-

atic validation or benchmarking is needed to make sure that the board is manufactured as designed, measurements are taken properly and, finally, that the interconnect analysis software provides acceptable accuracy. It is a whale of a project, if you do it yourself from scratch. Though, the process can be facilitated if you start with a readily available validation platform such as CMP-28/32 from Wild River Technology [2]. The platform was designed to illustrate and facilitate systematic analysis-to-measurement validation process at 28-32 Gbps and to demonstrate that interconnects for 28–32 Gbps can be predictably designed. Use of such a platform saves time and lowers the risks by benchmarking against

known and already measured and simulated structures. The CMP-28 platform <sup>[2]</sup> and Simbeor electromagnetic signal integrity software <sup>[3]</sup> are used here to illustrate signal integrity software validation process for 28 Gbps interconnects. The validation process can be divided into three steps:

- 1. Measure S-parameters with VNA up to 50 GHz and qualify them with formal quality metrics and, optionally, compare with S-parameters measured by an expert.

- 2. Identify or confirm broadband dielectric and conductor roughness models.

3. Simulate all test structures with the identified material models and verified board design adjustments and compare with the measured data in frequency and time domains.

### **Validation platform**

A validation platform is a very important tool for signal integrity software benchmarking or formal pre-qualification. Accuracy and limitations of the software can be easily identified with the analysis to measurement comparisons

on a typical set of interconnect

structures. A validation platform can be either developed in-house or purchased from a vendor. One of the industryfirst validation platforms was the physical layer reference design board (PLRD-1) from Teraspeed Consulting Group [4]. Use of the PLRD-1 revealed the need and enabled development of the industry-first broadband dielectric and conductor roughness models in Simbeor software. Another example of validation platform is the CMP-28/32 channel modeling platform from Wild River Technology [2]. Both CMP-28 and 32 versions contain 27 microstrip and stripline interconnect structures. All structures are equipped with either 2.92 mm (CMP-28) or 2.4 mm (CMP-

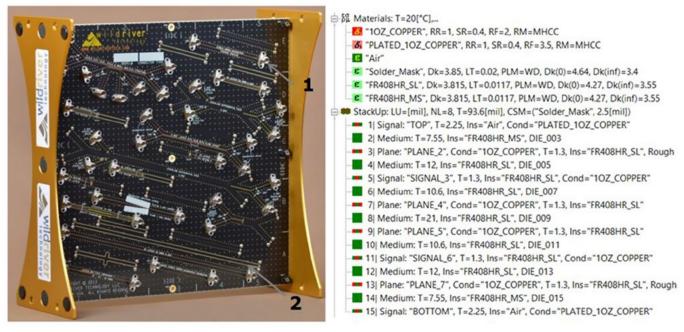

32) connectors to facilitate accurate measurements with a VNA. The CMP-28/32 platform is shown in Figure 1 and will be used here to demonstrate the systematic approach to the analysis to measurement correlation.

The CMP-28/32 platform contains multiple single-ended and differential line segments, suitable for identification or confirmation of material models, and also serve as the simplest validation structures. It also contains practical stripline and microstrip link paths with vias and crosstalk. In addition, it has a set of resonant structures to validate analysis of t-lines with different widths and do validation for highly reflective interconnects [2, 5].

and crosstalk.

Figure 1: CMP-28/32 channel modeling platform with 27 structures to benchmark software with stackup and broadband dielectric and conductor roughness models identified in Simbeor software [5].

### Step 1: S-parameters measurement and pre-qualification

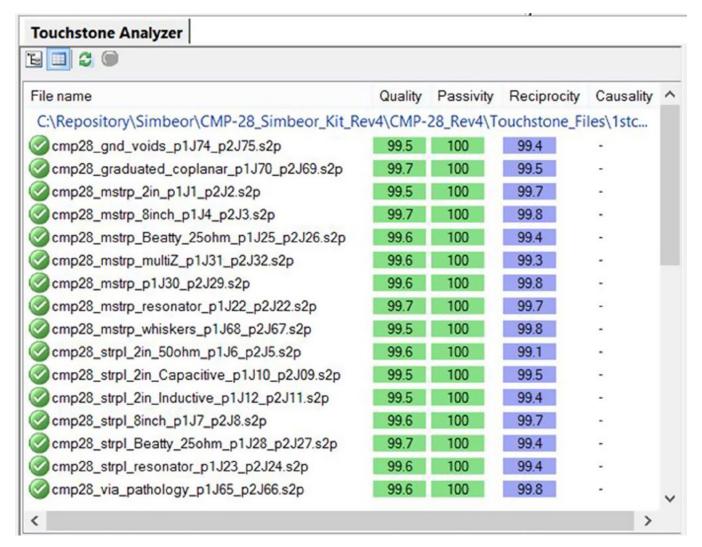

The first step in the systematic validation process is to make S-parameter measurements with VNA up to 50 GHz for 28-32 Gbps data rates and pre-qualify them for further analysis. For the reference, the CMP-28/32 kit includes S-parameter in Touchstone format measured for all structures by an expert with SOLT calibration up to the SMA connector. We will start with the example of formal pre-qualification of these measured data. The process is described in details in [1, 6]. We start with preliminary estimation of the passivity, reciprocity and causality metrics computed for discrete and bandwidth limited datasets. All metrics conveniently range from 0 (bad) to 100 (excellent) and further subdivided into bad, questionable, acceptable and good intervals as described in [6]. If all metrics fall into acceptable (blue) or good (green) intervals, we proceed and estimate the final quality metrics with the rational approximation or rational compact model. Models measured with high quality allow rational approximation with high accuracy—the root mean square error of such approximation can be used to construct the final quality metric [1, 6]. The end result of the measured S-parameters quality evaluation in Simbeor software is shown in Figure 2. All models measured by the expert pass the final quality test (Quality column).

Note that the frequency-continuous approximation of the discrete Touchstone models with the rational compact models is 100% causal by definition, because of the passivity is ensured by the software from DC to infinite frequency in this process. Such models are usable not only for the original Touchstone model quality evaluation, but also for further validation in time domain-fast and accurate computations of TDR/TDT and eye diagrams.

### Step 2: Broadband material model identification

After S-parameters are measured and prequalified, the next step is to identify broadband dielectric and conductor roughness models. The model identification with generalized modal Sparameters (or GMS-parameters) is the simplest and most accurate way to do it [7-9]. It requires S-parameters measured for two line segments with different length. Line of any type with any impedance can be used. It also does not require modelling of the connectors and launches. The

Figure 2: Example of formal quality evaluation in Simbeor software for a subset of S-parameters measured for CMP-28 platform.

CMP-28/32 platform contains 2- and 8-inch segments of single-ended stripline and microstrip traces and 2- and 6-inch segments of differential stripline and microstrip traces that can be used to extract or confirm dielectric and conductor roughness models.

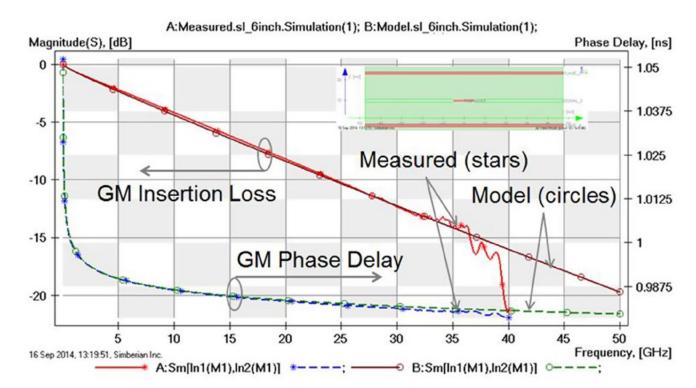

We start with the single-ended stripline and first extract reflectionless GMS-parameters for 6-inch segment from the measured data shown in Figure 3 (red and blue lines with stars). The useful range of the GMS-parameters is about 30 GHz for the insertion loss and 40 GHz for phase delay (restricted by the manufacturing variations). Next we build a model of a 6-inch stripline segment with quasi-static field solver

and first define dielectric model as the wideband Debye (AKA Djordjevic-Sarkar) [7] with dielectric constant Dk=3.66 and loss tangent LT=0.0117 as specified for Isola FR408HR material at 1 GHz.

To match the measured and modeled phase delay as shown in Figure 3, the Dk in the model needed adjustment from 3.66 to 3.815. This adjustment can be explained by the anisotropy of the composite dielectric. To match measured and modeled generalized modal insertion loss, we have two choices—increase the loss tangent or model conductor roughness. We choose to simulate conductor roughness with the simplest Modified Hammerstad model [7], defined

# The Absolute Best Value in High Technology Printed Circuit Boards

Since 1979, Eagle Electronics Inc. has provided our Customers with the highest quality Printed Circuit Boards at fair and competitive prices. We are committed to exceeding our Customers' expectations and requirements, acheiving total customer satisfaction on each and every job. It's just the way we do business!

With Eagle, you can expect:

- Rapid Response to Quote Requests

- Fair and Competitive Pricing/Costs

- 100% Quality Performance

- 100% On-Time Delivery Performance

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

- Thorough follow-up after job completion

- Total Satisfaction!

click here for a virtual tour of our facility!

www.eagle-elec.com

Figure 3: GMS parameters computed from S-parameters measured for 2- and 8-inch stripline segments (red and blue lines) and modeled for 6-inch stripline segment (brown and green lines) with wideband Debye dielectric model with Dk=3.815, LT=0.0117 @ 1 GHz, and Modified Hammerstad conductor roughness model with SR=0.4 um, RF=2.

by two surface roughness (SR) and roughness factor (RF) parameters. It is applied to the conductor surface impedance in the model. SR=0.4 um and RF=2 produced perfect good for the generalized modal (GM) insertion loss as shown in Figure 3.

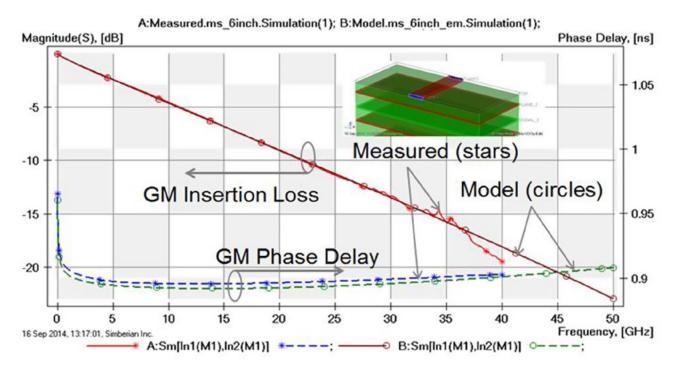

FR408HR model identified with the stripline should also work for the microstrip line. It can be validated with the GMS-parameters computed from the measured S-parameters of 2 and 8 inch microstrip line segments and shown in Figure 4. The 6-inch segment model is constructed with the electromagnetic solver to capture the highfrequency dispersion seen as the upward trend in the phase delay in Figure 4. In addition we define solder mask model as the wideband Debye with the values taken from the manufacturer specification: Dk=3.85 and LT=0.02 at 1 GHz. Good match of the phase delay can be observed in Figure 4. To match measured and modeled GM insertion loss, the conductor roughness parameters for the microstrip line needed adjustment of the roughness factor from 2 to 3.5. That concludes the material model identification. The process is automated in Simbeor software and typically takes 5-10 minutes.

As an optional, but recommended step, GMSparameters extracted from S-parameters measured for 2- and 6-inch differential links can be further used to confirm (or further adjust) the models extracted with the single-ended lines as demonstrated in [5].

Note that the identified dielectric and conductor roughness models are simple frequencycontinuous expressions [7]. The models are not just tables of Dk and LT frequency points and do not end where the measured data end. The extracted models are expected to be sufficiently accurate from DC up to 40 GHz and well above that frequency—the validation step will confirm it.

### Step 3: Analysis-to-measurement validation

After the S-parameters are measured and pre-qualified and broadband material models

Figure 4: GMS parameters computed from S-parameters measured for 2- and 8-inch microstrip line segments (red and blue lines) and modeled for 6-inch microstrip line segment (brown and green lines) with the same FR408HR model as for the stripline and wideband Debye model for solder mask with Dk=3.85, LT=0.02 @ 1 GHz and Modified Hammerstad conductor surface roughness model with SR=0.4 um, RF=3.5.

are identified, the final step is to run the postlayout analysis on all 27 structures on the validation platform and compare magnitude and phase of S-parameters, TDR and eye diagrams for 28 Gbps signals. Note, that before proceeding with the post-layout analysis and even before the material model identification step, all stackup and trace width adjustments made by the PCB manufacturer must be discovered. If no information is available, the board has to be cross-sectioned to proceed further. PCBs are rarely manufactured as they appear in your favorite layout tool, but a post-layout analysis tool usually takes geometry directly from the board design files. Changes in stackup, trace width and shape, and via back-drilling have to be verified and applied to the interconnect geometry consistently before running any analysis. Believe it or not, even the most accurate electromagnetic solver will produce garbage results without proper geometry description. Note that these manufacturing variations introduce additional uncertainties, and they usually cause discrepancies at frequencies above 20–30 GHz and so far cannot be properly accounted for.

The validation can be done in two ways: for just the PCB interconnect part with de-embedded connectors, or for complete link paths with the connectors and optionally adapters (exactly as measured in step 1). De-embedding is the additional step that can be problematic and errorprone. From the earlier validation experience [4] we have learned that the de-embedding of PCB structures with TRL procedure produces acceptable results only for highly reflective structures such as resonators or highly reflective vias. The highly reflective structures can be used to validate the software, but they are not typical for the actual interconnects with the minimized reflection. TRL de-embedding produces large errors in the reflection for the typical low-reflective structures. It makes it difficult or even practically impossible to use TDR for the valida-

tion. This is due to large manufacturing and dielectric properties variations in the test fixtures typical for PCB realm.

Thus, we proceed with the second option: validation for the complete link path. All measurements for the step 1 were done with the 2.92 mm SMA connectors and 2.92 to 2.4 coaxial adapters; no models were available for both. To overcome this obstacle, the model of the connector with the adapter was simply synthesized from S-parameters measured for two connectors and two adapters connected symmetrically back-to-back. We used cascaded connection of four coaxial sections to model adapter and connector and then matched both magnitude and phase of the reflection and transmission of the measured S-parameters and the circuit model of the back-to-back structure [5]. In addition, models for all launches (PCB part) were built with the 3D electromagnetic solver as a part of the post-layout electromagnetic decompositional analysis in Simbeor. That eliminated the errorprone de-embedding step.

Technically, comparison of the magnitudes and phases of S-parameters is sufficient to either make a decision on the accuracy or spot a problem. However, comparison in time domain is usually also needed and may reveal additional

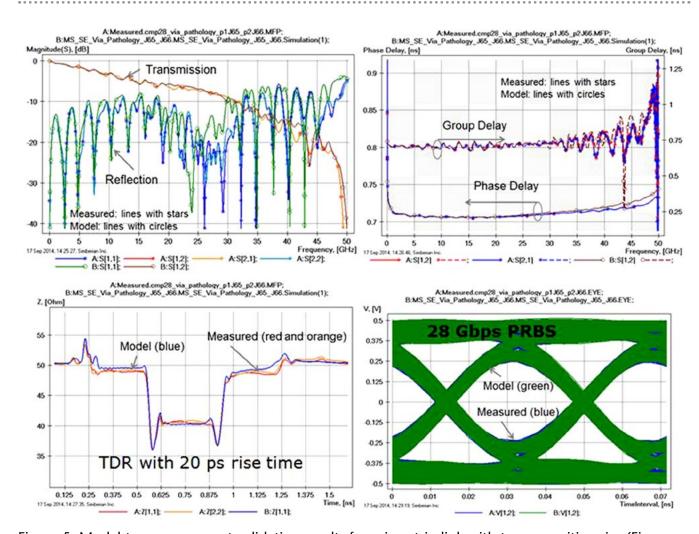

Figure 5: Model-to-measurement validation results for microstrip link with two capacitive vias (Figure 1, structure 1): Magnitudes of the transmission and reflection parameters (top left); group and phase delays of the transmission (top right), TDRs computed with 20 ps rise time Gaussian step (bottom left); eye diagrams for 28 Gbps PRBS signal (bottom right, on top of each other).

# Living proof that flying dragons are real!

# Dragon Circuits is proud to be at the forefront in unmanned aviation.

Interested in unmanned aerial or ground vehicles? Dragon Circuits is developing the newest technology to enhance vehicle run-time, performance and durability to put your company at the top of the industry. Proprietary electronics, built in the USA with ITAR, AS9100 and MIL-SPEC standards. Contact us for more information on a range of services from design, manufacturing, and even flight school!

problems. Comparison with TDR/TDT response that is measured directly with TDR scope requires modeling with the step function with the shape and spectrum matching to one used in the experiment. Similar situation is with the eye diagrams. Use of the ideal ramp step functions or PRBS with ideal trapezoidal shaped pulses may obfuscate and distort the results. Alternatively, measured and modeled S-parameters should be used to do all time domain computations with exactly the same stimuli matching the bandwidth of the model.

This can be done in two ways: either with convolution with the impulse response computed directly from discrete S-parameters with IFFT, or with the rational approximation and fast recursive convolution as it is done here. The rational approximation is frequency-continuous and naturally extends S-parameters to DC and to infinite frequencies. It is also causal by definition if passivity is ensured. The accuracy of the time domain analysis in this case is defined only by the accuracy of the rational approximation. In other words, the accuracy is always under control, unlike in case of analysis with IFFT where interpolation and extrapolation introduce uncontrolled errors. In addition, the recursive convolution is exact for piecewise linear signals and

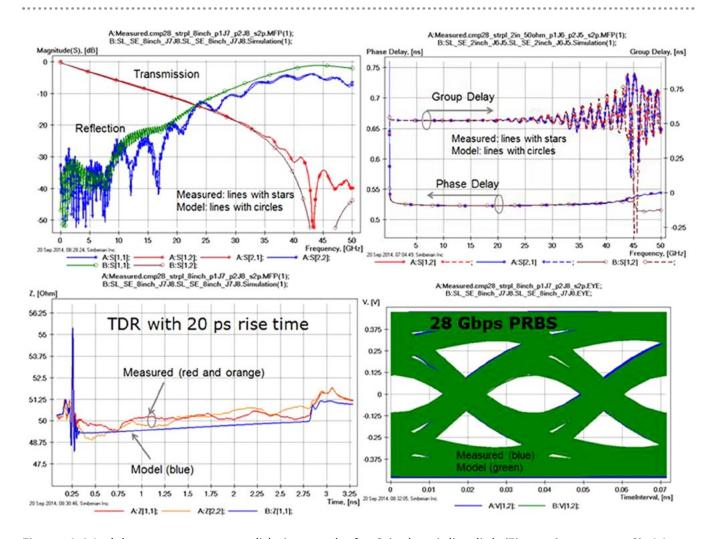

Figure 6: Model-to-measurement validation results for 8-inch stripline link (Figure 1, structure 2): Magnitudes of the transmission and reflection parameters (top left); group and phase delays of the transmission (top right), TDRs computed with 20 ps rise time Gaussian step (bottom left); eye diagrams for 28 Gbps PRBS signal (bottom right, on top of each other, literally).

much faster than the direct convolution. Thus, we will naturally use rational approximation for all time-domain computations here.

After all modeling decisions on what to compare and how to compare are made, we run the post-layout analysis for all 27 structures on the CMP-28 platform and compare the magnitudes of S-parameters, phase and group delays (and optionally phases), TDR computed with Gaussian step with 20 ps 10-90% rise time and eye diagrams computed with PRBS signal with 25 ps rise and fall time generated with LFSR with order 32. Two examples of the validation are shown in Figure 5 and Figure 6.

Results for microstrip line link with two capacitive vias (Figure 1, structure 1) are shown in Figure 5. It contains connectors with adapters on both ends, microstrip launches with throughhole vias, two segments of microstrip line with about 50 ohm impedance, two vias and one segment of wide microstrip line in the middle. The link is not optimal by design and represents highly reflective structure. We can conclude that the correlation is very good in this case and all discrepancies may be explained by the manufacturing and material properties variations.

Results of validation for a relatively low-reflective structure are shown in Figure 6. It is a simple 8-inch segment of single-ended stripline with launches, connectors and adapters on both ends (Figure 1, structure 2). The launches in this case are back-drilled with the goal to have less than 10-mil via stubs. Though, the manufacturer specified that the stubs may have +- 5 mil variation. 10-mil stubs were used in the model. Considering this and other types of variations, the correlation is acceptable. See all details of the analysis and analysis-to-measurement correlation for all 27 structures on CMP-28 platform in Reference [5].

### Conclusion

A systematic process of the analysis-tomeasurement validation up to 50 GHz is introduced here. The process is illustrated in this article with the CMP-28/32 validation platform and Simbeor software. Note that the validation problems can fall into three categories: manufacturing, measurement, and analysis, and only measurement quality and the interconnect analysis parts are covered here. Following the procedure, you can easily qualify or reveal problems in your signal integrity software of choice. Just try to do the analysis of all 27 test structures on CMP-28/32 validation platform and swim at 28 Gbps and beyond.

Do not forget to compare the productivity and cost of the tools. Finally, is your software qualified for the analysis of PCB interconnects running at 50 Gbps? The question is rhetorical so far. **PCBDESIGN**

### References

- 1. Y. Shlepnev, Measuring correlation to 50 GHz and beyond, The PCB Design Magazine, February 2013, p. 10-21.

- 2. CMP-28/32 Channel Modeling Platform with Simbeor EDA Kit, Wild River Technology.

- 3. Simbeor Electromagnetic Signal Integrity Software, Simberian Electromagnetic Solutions.

- 4. Y. Shlepnev, A. Neves, T. Dagostino, S. McMorrow, Measurement-Assisted Electromagnetic Extraction of Interconnect Parameters on Low-Cost FR-4 boards for 6-20 Gb/sec Applications, DesignCon 2009

- 5. Guide to CMP-28/32 Simbeor Kit, 2014.

- 6. Y. Shlepney, Reflections on S-parameter Quality, IBIS Summit at DesignCon 2011,

- 7. Y. Shlepnev, PCB and package design up to 50 GHz: Identifying dielectric and conductor roughness models, The PCB Design Magazine, February 2014, p. 12-28.

- 8. Y. Shlepnev, System and method for identification of complex permittivity of transmission line dielectric, US Patent #8577632, Nov. 5, 2013, Provisional App. #61/296237 filed on Jan. 19, 2010.

- 9. Y. Shlepney, System and method for identification of conductor surface roughness model for transmission lines, Patent Pending, App. #14/045,392 filed on Oct. 3, 2013.

Yuriy Shlepney, Ph.D., is founder and president of Simberian Inc. He previously served as principal engineer at Mentor Graphics and director of the Electromagnetic Group at

Eagleware Corporation.

### **BEYOND DESIGN**

# Signal Integrity, Part 1 of 3

by Barry Olney

IN-CIRCUIT DESIGN PTY LTD

As system performance increases, the PCB designer's challenges become more complex. The impact of lower core voltages, high frequencies and faster edge rates has forced us into the high-speed digital domain. But in reality, these issues can be overcome by experience and good design techniques. If you don't currently have the experience, then listen-up. This threepart series on signal integrity will cover the following topics:

- 1. How advanced IC fabrication techniques have created havoc with signal quality and radiated emissions.

- 2. The effects of crosstalk, timing and skew on signal integrity.

- 3. Where most designers go wrong with signal integrity and how to avoid the common pitfalls.

Technology is moving fast and much has changed over the past 25 years that I have been involved in high-speed multilayer PCB design. Particularly, advances in lithography enable IC manufacturers to ship smaller and smaller dies on chips. In 1987, we thought that 0.5 micron technology was the ultimate, but today 22 nm technology is common.

Also, power consumption in FPGAs has become a primary factor for FPGA selection. Whether the concern is absolute power consumption, usable performance, battery life, thermal challenges, or reliability, power consumption is at the center of it all. In order to reduce power consumption, IC manufacturers have moved to lower core voltages and higher operating frequencies, which of course mean faster edge rates. However, faster edge rates mean reflections and signal quality problems. So even when the package has not changed and your clock speed has not changed, a problem may exist for legacy designs. The enhancements in driver edge rates have a significant impact on signal quality, timing, crosstalk, and EMC.

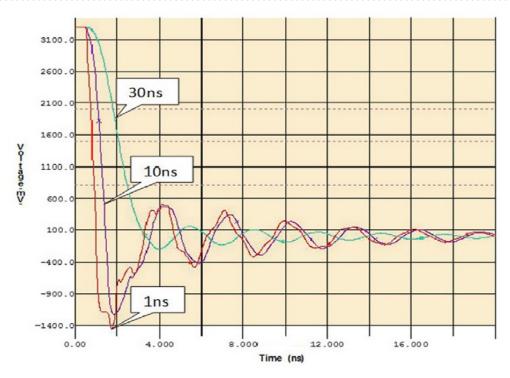

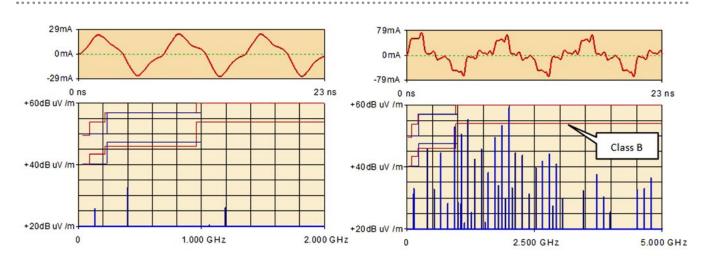

Figure 1 illustrates the change in edge rates over the years, from 10ns back in 1985 to less than 1ns in 2010. The faster edge rate for the same frequency and same length trace creates ringing in the un-terminated transmission line. This also has a direct impact on radiated emissions. Figure 2 shows the massive increase in emissions from the slowest to fastest rise time. When dealing with 1ns rise times, the emissions can easily exceed the FCC/CISPR Class B limits for an un-terminated transmission line.

At high frequencies, a trace on a PCB acts

# Quality PCBs from the established industry leader

With over 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits® is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for over 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

as a monopole or loop antenna. Unfortunately, the high-frequency components of the fundamental radiate more readily because their shorter wavelengths are comparable to trace lengths (particularly stubs), which act as antennas. Consequently, although the amplitude of the harmonic frequency components decrease as the frequency increase, the radiated frequency varies depending on the antennas/traces characteristics.

Computer-based products tend to radiate on the odd harmonics. High emissions are generally detected at the 3<sup>rd</sup>, 5<sup>th</sup> and sometimes the 7th harmonic of the fundamental clock frequency. If this also occurs where the AC impedance of the power distribution network is high, then the radiation is even higher. So at what speed should there be concern about wave propagation rather than just the current in conductors?

Figure 1: Edge rate changes over the past 25 years.

Figure 2: Radiated emissions from the 10ns edge rate (left) and 1ns (right).

**Rule of thumb:** Transmission line effects become an important design consideration when the trace length approaches 1/6 of the wavelength of the signal being transported. If the system clock frequency is 300 MHz, then the wavelength in FR-4 is about 0.5 m.

Impedance is the key factor that controls the stability of a design—it is the core issue of the signal integrity methodology. At low frequencies, a PCB trace is almost an ideal circuit with little resistance, and without capacitance or inductance. Current follows the path of least resistance. But at high frequencies, alternating current circuit characteristics dominate causing impedance, inductance and capacitance to become prevalent. Current then follows the path of least inductance. The impedance of an ideal lossless transmission line is related to the capacitance and inductance:

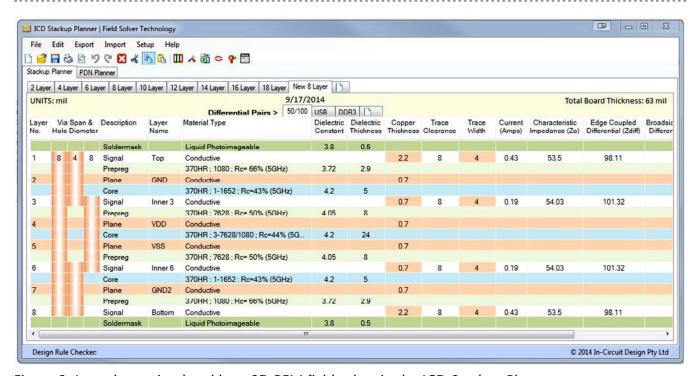

But this is very simplistic and the impedance should be simulated by a field solver (Figure 3) to obtain accurate values of impedance for each signal layer of the substrate. The impedance of the trace is extremely important, as any mismatch along the transmission path will result in a reduction in quality of the signal and possible radiation of noise. For perfect transfer of energy, the impedance at the source must equal the impedance at the load. However, this is not naturally the case and terminations are generally required at fast edge rates to limit ringing.

The configuration of the PCB stackup depends on many factors. But whatever the requirements, one should ensure that the following rules are followed in order to avoid a possible debacle:

- All signal layers should be adjacent to and closely coupled to an uninterrupted reference plane, creating a clear return path and eliminating broadside crosstalk.

- There is good planar capacitance to reduce AC impedance at high frequencies.

- High-speed signals should be routed between the planes to reduce radiation.

- The substrate should be symmetrical with an even number of layers. This prevents the PCB from warping during fabrication and reflow.

- The stackup should accommodate a number of different technologies.

- Cost (the most important design parameter) should also be addressed.

Figure 3: Impedance simulated by a 2D BEM field solver in the ICD Stackup Planner.

As signal rise times increase, consideration should be given to the propagation time and reflections of a routed trace. If the propagation time and reflection from source to load are longer than the edge transition time, an electrically long trace will exist. If the transmission line is short, reflections still occur but will be overwhelmed by the rising or falling edge and may not pose a problem. But even if the trace is short, termination may still be required if the load is capacitive or highly inductive to prevent ringing. Note that series terminators are the most effective for highspeed design.

For a driver signal with a 1ns rise time, since the speed of a signal in FR-4 is approximately 6in/ns (150mm/ns), then an un-terminated trace can only be  $6 \times 1/6 = 1.0$  inches (25mm) before reflections occur and termination is required.

Rule of Thumb: All drivers, whose trace length (in inches) is equal to or greater than the rise time (in ns), must have provision for termination.

In order to terminate a transmission line, one first needs to know the impedance of the driver and the transmission line. So how do we find this information? First of all an accurate field solver, such as the ICD Stackup Planner is required to determine the impedance of the PCB traces. Then, the source impedance must be extracted from the IBIS model. Subtracting the source impedance from the trace characteristic impedance gives the required series terminator value. Further details on how to find the source impedance in the IBIS model can be found in a previous column Beyond Design: Impedance Matching: Terminations.

Differential pairs are frequently used in high-speed design to provide noise immunity on serial interconnects. A differential pair is two complementary transmission lines that transfer equal and opposite signals down their length. These lengths should be kept equal and they should be coupled evenly along the signals length where possible. Symmetry is the key to successfully deploying differential signals in high-speed designs. Maintaining the equal and opposite amplitude and timing relationship is the principle concept.

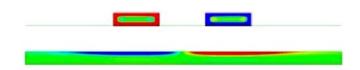

Figure 4: Return current of a microstrip differential pair. (courtesy of Ansoft)

Many people believe that since the two halves of the pair carry equal and opposite signals, that good ground connection is not required as the return current flows in the opposite signal. However, the return current actually flows in the reference plane below each trace. Figure 4, illustrates the return current of a microstrip pair flowing directly below each trace—just as is the case for a single ended transmission line. The only reason the pair of traces need to be coupled, is to reject common external noise.

If a differential pair can be routed closely coupled along the entire length, then consider using tight coupling. Otherwise, if the pair need to separate around an obstacle (a via for instance) then coupling the pair by twice the trace width is more effective. The reason being that a tightly coupled pair will increase impedance by 25% if separated while a more loosely couple pair will only vary by about 4% impedance. This provides more stable impedance along the trace length.

### **The rule of thumb:** Gap = 2x trace width.

Next month's column will continue to discuss signal integrity, in particular the effects of crosstalk, timing and skew on signal integrity so stay tuned.

### **Points to Remember**

- Advances in lithography enables IC manufacturers to ship smaller and smaller dies on chips.

- In order to reduce power consumption, IC manufacturers have moved to lower core voltages and higher operating frequencies, which of course mean faster edge rates.

- Faster edge rates mean reflections and signal quality problems.

# How can you find the best PCB Partner? We can tell you. We wrote the book on it.

Choosing a PCB partner isn't hard—if you know what to look for. We've broken it down into "The 5 Commandments" and you can download it for free.

We are proud to be the Circuit Board Manufacturer of more than 400 growing companies, and even prouder to be a good partner for all our customers!

Click to Download

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

- The faster edge rate, for the same frequency and same length trace, creates ringing in the un-terminated transmission line. This also has a direct impact on radiated emissions.

- Transmission line effects become an important design consideration when the trace length approaches 1/6 of the wave-length of the signal being transported.

- Impedance is the key factor that controls the stability of a design—it is the core issue of the signal integrity methodology.

- Any mismatch in impedance along the transmission path, will result in a reduction in quality of the signal and possibly radiation of noise.

- Series terminations are generally required at fast edge rates to limit ringing.

- All drivers, whose trace length (in inches) is equal to or greater than the rise time (in ns), must have provision for termination.

- Differential pair return current actually flows in the reference plane below each trace not in the opposite signal. PCBDESIGN

### References

- 1. Barry Olney's Beyond Design Columns: Practical Signal Integrity, Pre-Layout Simulation, Intro to Board-Level Simulation and the PCB Design Process, and Impedance Matching: Terminations.

- 2. Howard Johnson: High-speed Signal Propagation.

- 3. Henry Ott: Electromagnetic Compatibility Engineering.

The ICD Stackup and PDN Planner is distributed globally Altium.

Barry Olney is managing director of In-Circuit Design Pty Ltd (ICD), Australia. This PCB design service bureau specializes in board-level simulation, and has developed the ICD Stackup Plan-

ner and ICD PDN Planner software. To read past columns, or to contact Olney, click here.

### video interview

### **Embedded Components Standard Update**

by Real Time with... **SMTAI**

Vern Solberg of Solberg Technical Consulting updates us on the status of IPC-7092, the standard that focuses on embedding passive and active components. He explains why US board shops have been slow to embrace embedding components in board layers, though he is seeing a change as companies try to keep work from going overseas.

## INTRODUCING COOLSPAN® TECA

thermally & electrically conductive adhesive

### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

> **CONTACT YOUR SUPPORT TEAM TODAY**

www.rogerscorp.com

### MEET YOUR COOLSPAN® **TECA FILM SUPPORT TEAM**

Leading the way in...

• Support • Service • Knowledge • Reputation

### SCAN THE CODE TO GET OUR CONTACT INFO.

Dale Doyle Western Territory

John Dobrick

Scott Kennedy

John Hendricks

**Kent Yeung** Regional

Sales Director

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

## **PCB007 News Highlights**

### **IPC: Slump in PCB Sales and Orders is Typical for July**

"July is typically a slow month for the PCB industry and this year is no exception," said Sharon Starr, IPC's director of market research. "The PCB bookto-bill ratio has been hovering around 1.00 since February, which explains the flat year-to-date sales growth we are seeing," she added.

### **Molex Dongguan China Earns FDA Registration**

Molex Incorporated announced that the Molex Dongguan, China facility is now registered with the U.S. FDA as a compliant manufacturer of Class I medical devices. Part of an ongoing process improvement plan by the Molex printed circuit products group, registration confirms the Dongguan China site's adherence with FDA inspections, tracking, and traceability criteria.

### **Global PCB Market to Increase to** \$74.3B in 2018

IndustryARC forecasts the global PCB manufacturing market to increase its market size from around \$62.3 billion in 2013 to around \$74.31 billion in 2018, growing at a CAGR of 3.6%.

### **Murrietta, eSurface Ink Technology Licensing Agreement**

The executed technology license agreement between the two companies provides Murrietta the right to manufacture PCBs using eSurface's patented technology, receive implementation and marketing support from eSurface, and to be acknowledged as an eSurface authorized facility.

### **i3 to Provide Variety of Services** with New Contract

i3 Electronics Inc. has signed a multi-year agreement with an industry leading high-performance Computing firm for the supply of high-performance electronic assemblies. i3 will manufacture the PCBs and provide assembly, integration, and test services.

### **Precision Circuits West Unveils Line** of Aluminum PCBs

These aluminum PCBs (also called metal core PCBs) are five to ten times as thermally conductive as conventional epoxy-glass, at one-tenth of the thickness resulting in thermal transfer far more efficient than a conventional rigid PCB.

### **Intercept Strengthens Canadian Representation with Kaltron**

"Kaltron is delighted to offer Intercept's PCB, Hybrid IC, and RF software solutions to our customers in Canada. They complement very well our existing portfolio of design services, components, and modules," said Tom Martin, president of Kaltron.

### Multitest Leads the Way in 0.3 mm-pitch PCBs

Multitest can manufacture PCBs with 40+ layers at 0.35 mm in a single lamination process without the use of laser drilled, "stacked," blind vias.

### **Ibiden Receives Multilayer PCB Manufacturing Tech Patent**

The patent is mainly for a method of manufacturing a multi-layer printed wiring board including forming a core substrate, forming a first interlayer insulation layer over the core substrate, and forming a first filled via in the first interlayer insulation layer.

### **AT&S Among Top Performers in Resource Efficiency**

The Lean & Green jury highlighted particularly the data transparency and the culture of open communication within the company. AT&S is committed to a green strategy and sustainability is a major goal for all employees.

# What will you do with the space you is save

With the eSurface process, designers will have more freedoms with the type and size of substrates, opening up more avenues for new product creativity without compromising manufacturing viability.

### Key advantages include:

- Reduced production steps

- Higher yield on finer features

- No over-etching or under-etching

- Better signal integrity

- Ideal for RF/Microwave

- Higher density/reduced costs

- Reduce layers

- Reduce blind/buried vias

- Meets or exceeds Mil/IPC specs

Murrietta Circuits is proud to be an eSurface Licensed Manufacturer

**Click to learn more**

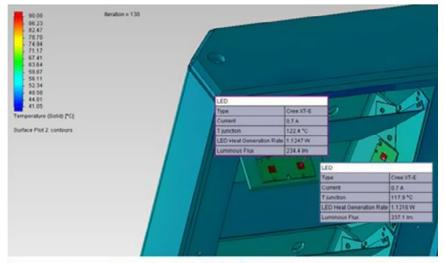

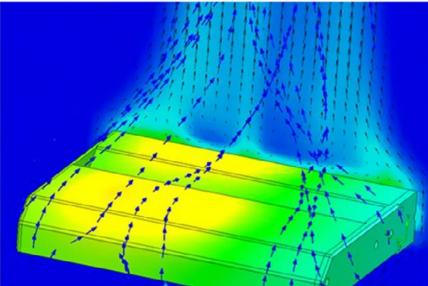

**by Dr. John Parry**MENTOR GRAPHICS

According to a June 2012 report from the Climate Group, many commercially available, outdoor light-emitting diode (LED) products offer high-quality light, durability, and significant electricity savings in the range of 50–70%. More European cities are adopting LED streetlights because LEDs can save energy costs, while exceeding local lighting standards. They last 50,000 to 100,000 hours, change little in color, and have a failure rate of around 1%, compared, for example, to up to 10% for ceramic metal halide fixtures over a similar time period. LED streetlights are a gateway technology when LED designers solve the current problems of reducing cost and thermal challenges, they'll be paving the way for wider adoption and the energy-saving potential of LEDs.

Thermal management is one of the more complex areas of LED system design. And until

a few years ago, the methods and technology to scientifically characterize the thermal behavior of the component, as well as its systems and subsystems, were not available. Instead, most engineers calculate their thermal needs from data sheets published by component manufacturers. Understandably, having data available to engineers on the specific thermal mechanics of LED-based devices within the system in which they are being used could be a huge step forward for future lighting designs.

This article describes a method that combines hardware measurement (a thermal transient tester), and computational fluid dynamics (CFD) software to provide high measurement throughput, which enables systems integrators to verify a vendor's thermal resistance data during design and to test incoming commercial off-the-shelf parts before they are introduced into production. This data can be used during the design and product development phase to accurately capture the thermal response of an LED lighting system.

# We deliver Advanced PCB Solutions!

## **Landless Via Technology**

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

**CLICK TO LEARN MORE**

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

# Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

**CLICK TO LEARN MORE**

## **Impedance Tolerance <5%!**

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

**CLICK TO LEARN MORE**

CANDOR INDUSTRIES, INC.

**ADVANCED PCB SOLUTIONS**

### THERMAL CHARACTERIZATION OF LEDS continues

### **Comprehensive LED Characterization**

The first step is to measure the LEDs that are generally suitable for the lighting application and to evaluate them by thermal and radiometric characterization. The LED must be measured as it transitions from a hot to cold state of operation to be able to thermally characterize it using the electrical test method. The results of such measurements are LED package thermal metrics and descriptive functions that will help design engineers understand the structure. The proper thermal design of the cooling solution can be created when the latest JEDEC LED thermal testing standards<sup>[1, 2]</sup> are used in this approach to identify the real thermal resistance and the real thermal impedance of the package. Also, not only the radiant power is measured and used in the thermal resistance-impedance calculations, but the temperature dependence of other light output properties such as luminous flux or color coordinates can also be measured. This way the best suitable LED can be selected from the various LED vendors for the design of a particular lighting application.

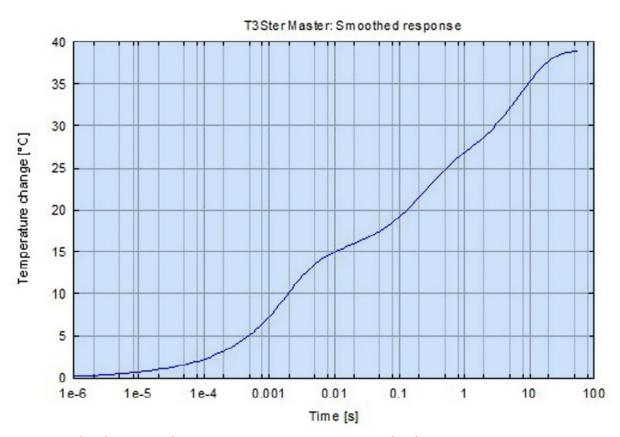

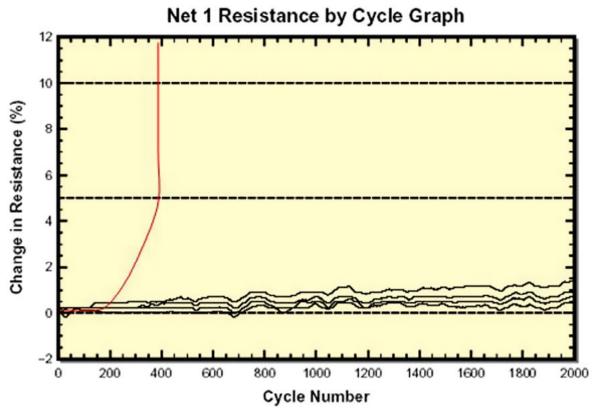

These testing standards were used in the development of LED-specific testing and measurement systems to provide comprehensive LED characterization, including thermal transient measurements and measuring almost all light output properties of LEDs. Figure 1 shows an example of an LED junction temperature transient measured on a cold plate—as the JESD 51-51 and JESD 51-52 standards recommend.

The measured junction temperature transient is turned into thermal impedance if it is divided by the applied heating power. In the case of LEDs, this is the supplied electrical power (forward voltage ' forward current) less the emitted optical power, also known as total radiant flux. The LED under test must be characterized optically to account for this. If the emitted optical power is not considered, the resulting thermal resistance will be smaller than reality.

Figure 1: Example of measured junction temperature transient of a device.

#### THERMAL CHARACTERIZATION OF LEDS continues

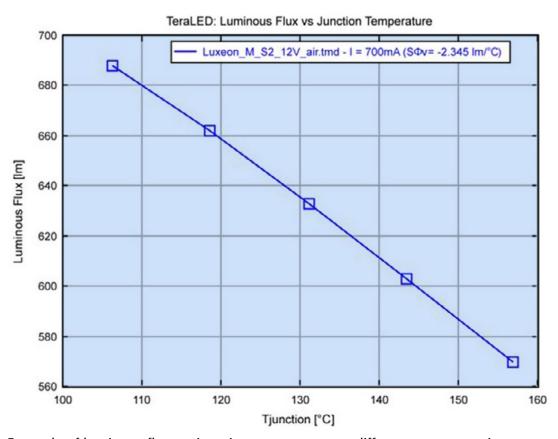

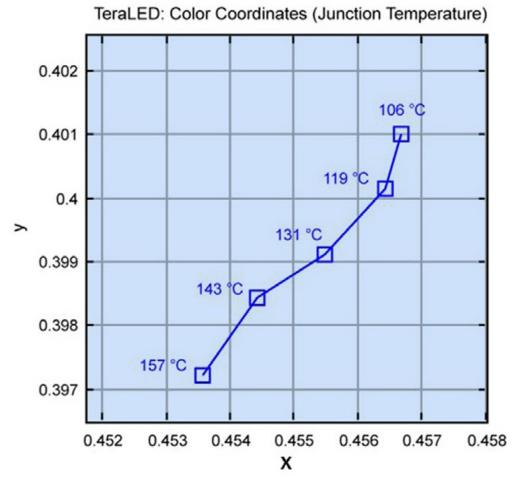

misleading the designers of the cooling solution. Measurement of the light output properties in combination with thermal tests as suggested, for example, by the JEDEC JESD 51-52 standard provides useful information about their temperature dependence (Figure 2). Figure 3 shows how the chromaticity of the measured LED changes with forward current and temperature.

The data processing software of the measurement system, T3Ster, derives structure functions from the transient measurement, which are then converted into models that are accurate in the case of packages that possess one-dimensional heat-flow path such as power LED packages[3]. Such models can be created as "side products" when the R<sub>thIC</sub> junction-tocase thermal resistance of the package under test is identified according to the latest JEDEC transient measurement standard (JESD 51-14), based on the so-called transient dual interface method[3].

#### **New Model for Simulating LED Thermal Re**sistance and Capacitance

This transient tester data can be used to more accurately simulate LED thermal characteristics by 3D CFD software, such as FloEFD, through an LED model, the so-called JEDEC 2R thermal resistor model in an extended format. For the 2R model, the necessary information can be found easily in the datasheets. In case of LEDs, the junction-to-bottom resistor of the 2R model is relevant; it is more or less equal to the R<sub>thIC</sub> junction-to-case thermal resistance of the package.

For the junction-to-top resistance of the 2R model, the junction-to-lens thermal resistance would be needed. This is usually not provided and it hardly can be correctly tested, and usually a sufficiently large value obtained from CFD simulations is provided. The way the standard 2R model is extended in the CFD software is that the junction-to-bottom part of the model is represented an RC model, which allows tran-

Figure 2: Example of luminous flux vs. junction temperature at different current settings.

#### THERMAL CHARACTERIZATION OF LEDS continues

Figure 3: Example of a chromaticity diagram for an LED generated by the TeraLED measurement system.

sient simulations because the thermal capacitance is also included in the model. However, the more detailed RC model requires more data of the LED, which often cannot be found in datasheets. In this case, the CFD tool makes it easier with an interface to the thermal characterization system.

A file can be exported out of the thermal transient tester's post-processing software that can be read by the CFD simulation tool with all the necessary data for the RC model in form of a Cauer-type ladder model. This file contains not just single thermal resistance and capacitance from junction to bottom  $(R_{jb}$  and  $C_{jb})$  values of the LEDs as a bulk value representing a single thermal time constant for the package, but represents the heat-flow path structure in details appropriate for accurate transient simulation using CFD analysis. For the proper prediction of the LED's hot lumens (luminous flux at operating junction temperature), an LED model in CFD also contains simple models for the radiant flux and luminous flux for constant drive currents of the LED. These models use the measured junction temperature sensitivity of these light output properties. Including the temperature sensitivity of these parameters is important to account for the complex, multi-domain operation of LEDs. Figure 4 shows results from the LED Compact Model in FloEFD provided for a given forward current using thermal data from thermal transient measurements by the T3Ster system.

Based on measured results from a validation experiment<sup>[4]</sup> to test this approach, it was clear that a simple reliance on datasheet values is insufficient when trying to determine the thermal performance of an LED system. Other meth**Privately Held Global Printed Circuit Board Fabrication**

# LOCAL SUPPORT

USA GERMANY JORDAN TAIWAN CHINA

Manufacturing at ANY Volume, both On and Offshore Quick Turn, Prototypes, DFM, Global Management Specialties like Rogers, Aluminum, Hybrid Materials Logistics including Consignment, VMI, JIT & More 24-7 Local Engineering, Service, and Support

**Download Digital Brochure**

**Download Our Capabilities**

#### **THERMAL CHARACTERIZATION OF LEDS** continues

ods provided information that there was a thermal issue with the LED packages under test; however, only the JESD 51-51 compliant transient test method provided a hint about the location of the problem. As well as being useful for failure analysis, this method can be used to derive an appropriate compact LED model which, when inserted into a simulation tool, can provide better predictions of LED operation. LED system designers will be able to rely on real measured component data, allowing them to make better judgments on their thermal designs. This capability will allow wider adoption and reduced costs with the energy-saving potential of LEDs. PCBDESIGN

#### References

- 1. JEDEC Standard JESD51-51, "Implementation of the Electrical Test Method for the Measurement of the Real Thermal Resistance and Impedance of Light-emitting Diodes with Exposed Cooling Surface," (April 2012).

- 2. JEDEC Standard JESD51-52, "Guidelines for Combining CIE 127-2007 Total Flux Measurements with Thermal Measurements of LEDs with Exposed Cooling Surface," (April 2012).

- 3. JEDEC Standard JESD51-14 "Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction-To-Case of Semiconductor Devices with Heat Flow Through a Single Path," (November 2010).

- 4. B. Marovic, "Efficient and Accurate Thermal Simulation by Combining Thermal and Radiometric Characterized LEDs with Computational Fluid Dynamics," International Symposium on Automotive Lighting, Sept. 2013, Darmstadt, Germany.

Figure 4: An example of the calculation done in the CFD simulation software using the LED Compact Model of the luminous flux, at operating junction temperature for the LEDs in a luminaire. (Image courtesy of OptimalOptik Ltd. and Budapest University of Technology and Economics, Budapest, Hungary.)

Dr. John Parry is electronics industry manager for the mechanical analysis division of Mentor Graphics. He serves on the JEDEC Thermal Standards Committee and on various

conference committees and was General Chair of the SEMI-THERM 21 conference.

#### PROTOTRON CIRCUITS TUCSON

Tucson, Arizona, U.S.A

Prototron Circuits

Quality Printed Circuit Boards

Overview

Contact

Specs

About

Videos

**Photos**

**Brochures**

News

Prototron Circuits is one of the industry's best and most reliable high technology quick turn companies in the country. With facilities in Redmond, WA and Tucson, AZ, Prototron is the quick turn printed circuit board manufacturer for people who value quality and on time delivery. Whether your need is a prototype PCB or medium volume production, our goal is to always deliver high technology "production quality" circuit boards on time.

With Prototron's strong engineering support, we can provide assistance with impedance calculations, as well as unique solutions to complex design issues.

Markets: Military/Aerospace

Board Types: Multilayer

Mfg Volumes: Prototype, Small, Medium

Other Services: Quick turn-around

Sequential lamination

0 9001, ITAR registered, MIL-PRF-5.

Blind/buried vias, Controlled Im

Click here to see a demo

#### Why YOU should Showcase:

- Capabilities listing for advanced search functionality

- Specialties and certifications listing

- Ability to upload brochures and videos

- Quick and easy "Contact" and "RFQ" buttons

- News, web and contact links

Click to see a partial list of registered OEMs!

www.thepcblist.com

# This is Sketch Routing, Part 2: Quality

#### by Charles Pfeil

**MENTOR GRAPHICS**

This is the second of three articles that discusses the core elements of effective PCB routing (control, quality, and performance). I recommend reading my last column on taking control, because it gives some background information that will help when reading this column.

PCB designers care about route quality and it is not just a matter of being artistic. Route quality is objective and subjective—both are essential to successful routing.

#### **Objective Quality**

Objective quality can be defined as fulfilling the fabrication and signal integrity requirements as defined. The intent of route quality for fabrication is to enable high board yields, high reliability and low cost. It is important to understand the critical elements required by the fabricator, then set up and follow the physical constraints that will satisfy the desired objectives. Interactive and automatic routing must follow these physical rules, otherwise the time spent preparing any moderately complex design for fabrication will be excessive.